#### **PAPER**

# DC and RF performance of lateral AlGaN/GaN FinFET with ultrathin gate dielectric

To cite this article: Doan Ylmaz et al 2022 Semicond. Sci. Technol. 37 085008

View the <u>article online</u> for updates and enhancements.

# You may also like

- <u>Strategic Review on Different Materials for</u> <u>FinFET Structure Performance</u> Optimization

- K Bindu Madhavi and Suman Lata Tripathi

- <u>FinFET Devices and Integration</u> Huiming Bu

- (Plenary) Physical Insights on the Design of UTB Devices, Including FinFETs Jerry G. Fossum

Semicond. Sci. Technol. 37 (2022) 085008 (11pp)

https://doi.org/10.1088/1361-6641/ac7818

# DC and RF performance of lateral AIGaN/GaN FinFET with ultrathin gate dielectric

Doğan Yılmaz<sup>1,2,\*</sup>, Oğuz Odabaşı<sup>3</sup>, Gurur Salkım<sup>2</sup>, Emirhan Urfali<sup>2</sup>, Büşra Çankaya Akoğlu<sup>2</sup>, Ekmel Özbay<sup>2,4</sup>, and Şemsettin Altındal<sup>1,5</sup>

E-mail: dogany@bilkent.edu.tr

Received 4 April 2022, revised 20 May 2022 Accepted for publication 13 June 2022 Published 23 June 2022

#### **Abstract**

In this study, an enhancement-mode (E-mode) GaN high electron mobility transistor (HEMT) with lateral tri-gate structure field effect transistor (FinFET) is proposed. To passivate the fin width, while keeping the normally-off performance of the FinFET intact, an ultrathin aluminium-oxide/sapphire (Al<sub>2</sub>O<sub>3</sub>) gate dielectric is proposed (in a basic single-finger 0.125 mm device). Later, the DC and radio frequency (RF) performances of the proposed FinFET designs (with optimized fin width and Al<sub>2</sub>O<sub>3</sub> thickness) are compared with that of conventional planar HEMT. DC and RF measurements are performed using power transistors in ten-fingers configuration, with a total gate periphery of 2.5 mm. The effect of Fin structure and  $Al_2O_3$  thickness on the electrical performance of HEMTs, including threshold voltage  $(V_{th})$ shift, transconductance  $(g_m)$  linearity, small-signal gain, cut off frequency  $(f_1)$ , output power  $(P_{\text{out}})$ , and power-added efficiency (PAE) are investigated. Based on our findings, FinFET configuration imposes normally-off functionality with a  $V_{th} = 0.2 V$ , while the planar architecture has a  $V_{\rm th} = -3.7~V$ . Originating from passivation property of the alumina layer, the FinFET design exhibits two orders of magnitude smaller drain and gate leakage currents compared to the planar case. Moreover, large signal RF measurements reveals an improved  $P_{\text{out}}$ density by over 50% compared to planar device, attributed to reduced thermal resistance in FinFETs stemming from additional lateral heat spreading of sidewall gates. Owing to its superior DC and RF performance, the proposed FinFET design with ultrathin gate dielectric could bear the potential of reliable operating for microwave power applications, by further scaling of the gate length.

Keywords: AlGaN/GaN Enhancement mode (E-mode), FinFET, gate dielectric, Al<sub>2</sub>O<sub>3</sub> MOS,  $V_{\text{th}}$  shift, DC and RF performance

1

(Some figures may appear in colour only in the online journal)

1361-6641/22/085008+11\$33.00 Printed in the UK

© 2022 IOP Publishing Ltd

<sup>&</sup>lt;sup>1</sup> Advanced Technologies, Gazi University, Ankara, Turkey

<sup>&</sup>lt;sup>2</sup> NANOTAM-Nanotechnology Research Center, Bilkent University, Ankara, Turkey

<sup>&</sup>lt;sup>3</sup> Department of Electrical and Computer Engineering, University of Michigan, Ann Arbor, MI, United States of America

<sup>&</sup>lt;sup>4</sup> Department of Electrical and Electronics Engineering, Bilkent University, Ankara, Turkey

<sup>&</sup>lt;sup>5</sup> Department of Physics, Faculty of Sciences, Gazi University, Ankara, Turkey

<sup>\*</sup> Author to whom any correspondence should be addressed.

#### 1. Introduction

In recent years, the demand for high-frequency/highpower operation in the wireless data communication and microwave technology market has highlighted the superiority of AlGaN/GaN high electron mobility transistors (HEMTs). Stemming from GaN's excellent material properties (compared to Si and GaAs), such as high bandgap, large thermal conductivity, high critical breakdown voltage, and high-power density, commercial GaN based devices have attracted intensive attention in consumer electronics, electric vehicles, and defense applications. Besides all these advantages, the performance limits of GaN have not been reached yet, and therefore, significant studies are still ongoing to optimize its operation. Essentially, the epitaxial growth for GaN HEMT transistors is performed in three main substrates, including SiC, Si, and sapphire, defined based on the requirements and applications [1-3]. Because of the polarization-induced charge formation at the GaN/AlGaN interface, traditional GaN-based HEMTs are inherently normally-on devices, or so called depletion-mode (D-mode) devices, with large twodimensional electron gas (2DEG) density at zero gate bias. However, for the power electronic industry, especially for switching devices, enhancement-mode (E-mode) transistors are required for safe, simple and fail-free circuit operation conditions [4–6].

There are several approaches to achieve E-mode operations, including: (a) fluorine plasma treatment, (b) p-GaN gate, and (c) recess gate [7, 8]. However, all these methods have their own bottlenecks. In the plasma treatment approach, the negative F<sup>-</sup> ions deplete electrons from the channel and shifts the threshold voltage towards positive values. This shift depends on the radio frequency (RF) power and exposure time to the plasma. Thus E-mode operations are obtained by charge storing, without reducing the channel conductance compare to other approaches [9–11]. However, the main drawback with this method is maintaining the  $V_{\rm th}$  stable in the thermal steps during the fabrication process. This is caused by fluorine out-diffusion, upon exposing to high temperature cycles. Moreover, the fluorine plasma treated HEMT exhibits low drain current and small transconductance which is related to the impact of plasma on the carrier concentration, mobility, and sheet resistance  $(R_s)$  [12]. For p-GaN approach, the obtainable threshold voltages are relatively limited to small positive voltage values and the gate leakages are comparably larger [13]. Additionally, the  $V_{\rm th}$  of p-GaN strongly depends on the doping concentration of p-GaN and the thickness of AlGaN. Hence, there is a trade-off between electron concentration and  $V_{\rm th}$  [14]. Besides this, there are still reliability and trapping issues, as normally-off p-GaN HEMTs are often affected by gate leakage current, when the gate is stressed at forward voltage. Finally, in the gate recess method, the region beneath of the gate contact is etched by a plasma etch process. The depth of the recess etch can be used to control the gate threshold voltage. However, the plasma etching process damages the epitaxial layer crystallinity and generates a large density of the dangling bonds. The reduced AlGaN layer thickness, together with the formation of trapping states, significantly reduce the 2DEG density and DC performance of the device. Moreover, the nanometer scale uncertainty on the etching depth causes repeatability issues. It should be mentioned that these two techniques also increase the transistor On resistance ( $R_{\rm ON}$ ) [15]. Taking all into account, in an ideal platform, E-mode operation should be realized without sacrificing the device's DC and RF performance.

FinFET configuration could be a solution and in recent years, its usage started to dominate the GaN power device technology. FinFET has several advantages over the abovementioned approaches like E-mode operation, small On resistance, less gate and drain leakage, more linear transconductance  $(g_{\rm m})$  and higher output power density [16–20]. In this design architecture,  $V_{th}$  could be shifted toward a positive direction by shrinking the channel lateral width. Owing to its three-dimensional (3D) configuration, both top and sidewalls simultaneously deplete the gate region and therefore, better controllability is achieved compare to the planar HEMT. Indeed, recent studies have successfully fabricated E-mode FinFETs with fin widths below 100 nm [21–24]. This method is also preferred in applications where both E- and D-mode devices are on the same chip, as this can be achieved by adding a few fabrication steps compared to other normally-off HEMT methods. Recent studies report the fact that FinFETs can improve the current density and linearity of the transconductance, which is an important factor for RF power amplifiers due to the large dynamic range in the highly variable modulation signals [25–31]. However, similar to gate recess method, in FinFET, the gate walls are formed using plasma etching process and this process generates large density of surface trap states. These trap states mediate the current conduction between the gate and buffer/barrier layers and consequently lead to high leakage currents. Moreover, the existence of interface trap states, in gate-barrier interface, significantly degrade the RF performance of the device. Passivation of these trap states could be achieved using a proper oxide and nitride based passivation layer. However, these dielectric layer can suppress the fringing effects in sidewalls and lack of lateral depletion mechanism could lead to loss of E-mode operation. Thus, a fine trade-off in the dielectric layer thickness is needed to acquire both E-mode functionality and passivation in the Fin-FET device configuration [32, 33].

In general, atomic layer deposition (ALD) is used to obtain high-quality and high-dielectric thin film because of the layer-by-layer nature of its deposition kinetics [34]. High-performance metal-oxide-semiconductor (MOS) diodes and MOS field effect transistors can also be realized by combining GaN with high- $\kappa$  dielectric materials such as Ga<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub>, and Al<sub>2</sub>O<sub>3</sub> instead of conventional low- $\kappa$  SiO<sub>2</sub> as the gate dielectric [35–39]. Among these materials, sapphire is a very stable and robust material and also it has many favorable properties, including high- $\kappa$  dielectric ( $\sim$ 9), high-bandgap ( $\sim$ 7 eV), high-breakdown electric-field ( $\sim$ 10<sup>9</sup> V m<sup>-1</sup>), thermodynamic stability on the semiconductors up to high-temperatures [40].

In this study, a FinFET HEMT device, with ultrathin Al<sub>2</sub>O<sub>3</sub> layer, is designed and fabricated. The proposed design shows E-mode operation with threshold voltage of  $V_{\text{th}} = 0.2 \text{ V}$ .

Besides its E-mode operation, the use of optimal alumina layer thickness (which is 3 nm in our case) provides excellent DC and RF characteristics, outweighing the planar design. For this aim, first, single-finger 0.125 mm gate HEMT devices were fabricated and the impact of fin width and Al<sub>2</sub>O<sub>3</sub> thickness were investigated. The DC characterization are conducted to investigate the HEMTs DC characteristics, including  $V_{\rm th}$  shift, drain current density, gate turn on and gate leakages. The pulsed  $I_d$ – $V_d$  and  $I_d$ – $V_g$  measurements are done to understand the passivation perform. Based on these findings, at the optimum alumina thickness of 3 nm, we have achieved normally-off operation with near two orders of magnitude smaller gate leakage currents. It was found that thicker gate dielectric does not significantly change the leakage current, while it diminishes the E-mode operation of the Fin-FET. Moreover, thinner dielectrics cannot effectively passivate the surface dangling bonds. In the second part of the manuscript, the optimized trigate AlGaN/GaN HEMTs were fabricated with 80 nm fin width and 3 nm Al<sub>2</sub>O<sub>3</sub> thickness, in ten-fingers configuration, with a total gate periphery of 2.5 mm, drain-source distance of  $L_{\rm SD}=5~\mu{\rm m}$ , gate length of  $L_{\rm G}=0.8~\mu{\rm m}$ , and gate-source distance of  $L_{\rm SG}=1.5~\mu{\rm m}$ . DC and RF measurements are performed in these large-scale HEMT devices. According to our DC measurements, the FinFET design shows above two-fold enhancement in maximum drain current  $(I_d)$  and conductance  $(g_m)$ , compared to that of D-mode planar HEMT reference. Moreover, similar to small scale device, the gate and drain leakages are reduced by above two orders of magnitude. Moreover, loadpull measurements are performed to scrutinize the RF performance of the device. The obtained characterization results prove a more stable operation of FinFET, under large RF signal condition. The  $P_{\rm out}$  density is improved by 50% in FinFET HEMT.

## 2. Experimental

#### 2.1. Epitaxial structure

The AlGaN/GaN multilayer structure was grown by using metal organic chemical vapor deposition on a three-inch-diameter SiC substrate which includes 1.8  $\mu$ m GaN Buffer, a 0.8 nm AlN spike layer, a 20 nm undoped AlGaN barrier layer with Al content of 25% capped with 3 nm GaN. The channel electron mobility ( $\mu$ ), sheet resistance ( $R_s$ ), and the sheet carrier concentration ( $N_s$ ) are measured as 1890 cm<sup>2</sup> (V s)<sup>-1</sup>, 310  $\Omega$  sq<sup>-1</sup>, and 1.06  $\times$  10<sup>13</sup> cm<sup>-2</sup>, with the Lehighton contactless hall system, respectively.

# 2.2. Device fabrication

2.2.1. Single gate process. The fabrication of 0.125 mm HEMT starts with conventional Cl-based mesa isolation. The process continues with ohmic contact formation via deposition of a Ti/Al/Ni/Au multilayer metal stack. Before the ohmic annealing, e-beam alignment marks are defined as a negative etched marker. The etched mark is advantageous in the repeatability of electron beam (e-beam) lithography over

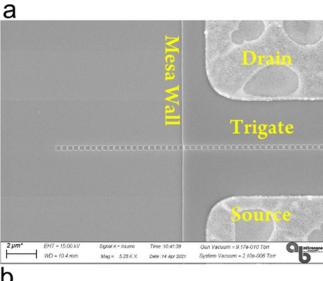

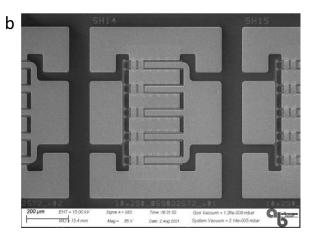

**Figure 1.** SEM images of (a) FinFET structure and (b) the single-gate HEMT device.

annealed metal with a rough surface. After defining e-beam alignment marks, the ohmic contacts are annealed at 850 °C in an N<sub>2</sub> gas environment for 30 s. Later, TLM method is used to measure contact resistance values which was found to be  $0.3~\Omega$  mm. In the case of FinFET device, the Fin structure is patterned in various widths by 100 keV e-beam lithography. ZEP 520 A e-beam resist is used due to its both high etch selectivity and high resolution. After the Fin lithography is defined, 50 nm deep Fin etch is done with Cl<sub>2</sub> based plasma (see figure 1(a)). The Al<sub>2</sub>O<sub>3</sub> thin films with different thicknesses of 1 nm, 3 nm and 5 nm were deposited by ALD. This Al<sub>2</sub>O<sub>3</sub> thin film also is used for the surface passivation. As the reference, one sample is left with no Al<sub>2</sub>O<sub>3</sub> gate dielectric. It means that there is no passivated access region for this sample. For this case only gate leakage is considered for a fair comparison. The gate is defined with copolymer/pmma bilayer by e-beam lithography again. Considering the S-band power transistor design, the thickness of gate metal and alignment accuracy, the gate footprint is optimized 0.8  $\mu$ m which is the same as the multi-gate footprint. The 450 nm Ni/Au gate

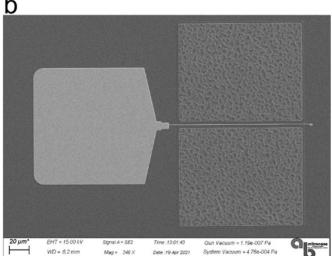

**Figure 2.** SEM images of (a) gate foot and Fin structures, and (b) fabricated multi-gate device with corresponding geometries. (c) 3D schematic of the fabrication route of FinFET including (i) Fin Etch, (ii)  $Al_2O_3$  deposition, and (iii) gate metalization.

electrodes are patterned by the e-beam evaporation and lift-off technique. During the evaporation, samples are also rotated to avoid shadow effects. For the parametric study of trigate structure, the 250 nm designed trench area is fixed to have uniform coating of the metal in the tri-gate sidewalls, considering the nickel (Ni) and gold (Au) grain sizes. Fin width is changed from 60 to 250 nm. It should be noted that for all the e-beam lithography processes that are described, a conductive polymer was spin coated on top to avoid charging. The scanning electron microscopy (SEM) image of fabricated single-gate device is shown in figure 1(b). After successful fabrication of both FinFET and planar HEMTS, DC and pulsed measurements are carried out for all samples. The details will be provided in upcoming sections.

2.2.2. Multi-gate process. In the other part of the study, the conventional and tri-gate AlGaN/GaN HEMTs were fully fabricated with optimized geometries of 80 nm Fin width and approximately 3 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric. These HEMTs consisted of 250  $\mu$ m ten-fingers transistors, drain-source distance of  $L_{\rm SD}=5~\mu{\rm m}$ , gate length of  $L_{\rm G}=0.8~\mu{\rm m}$ , gate-source distance of  $L_{\rm SG}=1.5~\mu{\rm m},\,W_{\rm fin}=80~{\rm nm}$  and  $W_{\rm trench}=320~{\rm nm}$ for 400 nm period, accumulating a total effective gate width of  $W_{\rm eff} = 500 \ \mu \rm m$ . (see figures 2(a) and (b)) For this multigate device, the same fabrication steps, as one followed in single-gate transistors, are applied until the end of the mesa step. After the mesa etching, the 75 nm 1st Si<sub>3</sub>N<sub>4</sub> passivation is formed to passivate the access region and to create the foot width in the T-Gate structure. Before the deposition, surfacecontrolled wet treatment is applied with hot ammonia solution to remove the oxide layer formed on the epi surface. Typical F- based gases are used to completely etch the film, the Si<sub>3</sub>N<sub>4</sub> layer has to be 30% over etched. One sample is continued after forming the gate foot with the optimized Fin width and Al<sub>2</sub>O<sub>3</sub> thickness.

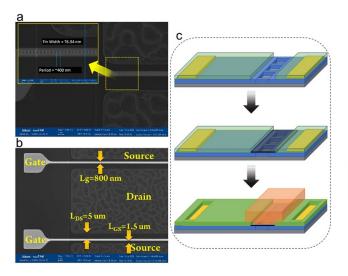

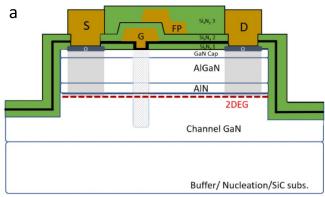

**Figure 3.** (a) The schematic illustration of device cross section, and (b) the SEM image of the final multi-gate HEMT device.

Ni (50 nm) /Au (400 nm) are deposition for the gate metal. The process flow is schematically illustrated in figure 2(c). Gate location, Fin, and trench width are checked with a SEM. The other one is the conventional planar HEMT which means there is no Fin and  $Al_2O_3$  deposition.

A 210 nm 2nd  $Si_3N_4$  layer is deposited between the gate and field-plate as passivation to suppress the formation of hot spot electric fields near the drain side of the gate and reduces gate-to-drain feedback capacitance. The first thick metal was formed by evaporation of Ti-Au. For protection,  $Si_3N_4$  was deposited over the samples by plasma-enhanced chemical vapor deposition (PECVD). Fabrication is finished with an air bridge and a 4  $\mu$ m thick metal deposition. A representative cross-sectional view of the device at the end fabrication is presented in figure 3(a). An SEM image of the fabricated device with a multi-gate periphery is shown in figure 3(b).

The focus of electron-beam lithography (EBL) is the main issue of the reliable and repeatable fabrication of sub100 nm periodic Fin pattern on the large size device. As is known, SiC samples are transparent semiconductors, that is, the focusing process of samples like this is quite challenging for systems that make height maps with laser. The issue can be ignored with no height, blind job, or reflective layer but all these techniques cause a resolution and focusing issue. In this process to expose the sub-100 multi-structure, the negative 20  $\mu m$  square EBL markers are used for focusing. With this method, we

succeed the same resolution and Fin size for all gate fingers on the  $10 \times 250~\mu m$  FinFET and also from sample to sample. Pattering is done with 100 keV acceleration voltage to minimize the proximity effect.

#### 3. Result and discussion

In the first step of the characterization part, DC measurements were performed for the single-finger HEMTs. The main purpose of this step is to analyze the impact of fin width and alumina thickness in device normally-off operation and gate leakage. Later, the optimal geometries are utilized to demonstrate multi-finger large-scale designs. For these devices, both DC and RF performances are evaluated. The upcoming section summarizes our findings. To understand the FinFET's performance, the effect of device geometry should be analyzed. For a fair comparison among devices, all device performance has to be normalized.

There are two factors that affect the electron concentration of the device, one is fin width  $(W_{\rm fin})$  and the other one is depletion of the electron because of the sidewall gate  $(W_{\rm dep})$ . The real channel width is  $W_{\rm fin}$ — $2W_{\rm dep}$  where  $W_{\rm dep}$  is fixed and is formed by the Schottky gate metal or gate-insulator-semiconductor. Devices have trenches on the active area and there is no electron concentration at the near sidewall [20, 41].

Tri-gate lateral GaN HEMT performance is independent of the Fin height ( $H_{\text{fin}}$ ) which is ignored because does not affect the sheet density.  $H_{\text{fin}}$  is important for a Silicon on Insulator FinFET device [42].

In the literature, the widely accepted normalization method for laterally GaN HEMTs is to calculate the effective channel width  $(W_{\rm eff})$  with total electron concentration which only change with the total active region. Therefore,

$$W_{

m eff} = W_{

m fin} imes n,$$

$W_{

m channel} = (W_{

m fin} + W_{

m trench}) imes n,$

*n* is number of Fin. And filling factor (*FF*) is given by  $W_{\text{fin}}/(W_{\text{fin}} + W_{\text{trench}})$ .

Based on this,  $W_{\rm eff}$  is also calculated as (total  $L_{\rm g}$ )  $\times$  FF [43–47].

All measured values are normalized by effective gate width.

# 3.1. DC performance of single gate devices

As already stated above, the samples in the first set of experiments were evaluated for  $V_{\rm th}$  shift and leakage current performance. For the FinFET design, the Fin width was spanned from 60 to 250 nm. Additionally, the Al<sub>2</sub>O<sub>3</sub> thickness was chosen to be 1, 3 and 5 nm. Initially, the Fin width is fixed at 80 nm and three different Al<sub>2</sub>O<sub>3</sub> gate dielectrics are fabricated and compared with the reference planar design. Table 1 summarizes the threshold voltage for all the studied cases. In the conventional planar HEMTs, the threshold voltage is negatively shifted from -3.48 to -4.11 V, as we move from bare device (with no gate dielectric) to 5 nm-thick alumina dielectric gate structure. These values are significantly shifted toward positive values, in the FinFET design, mainly

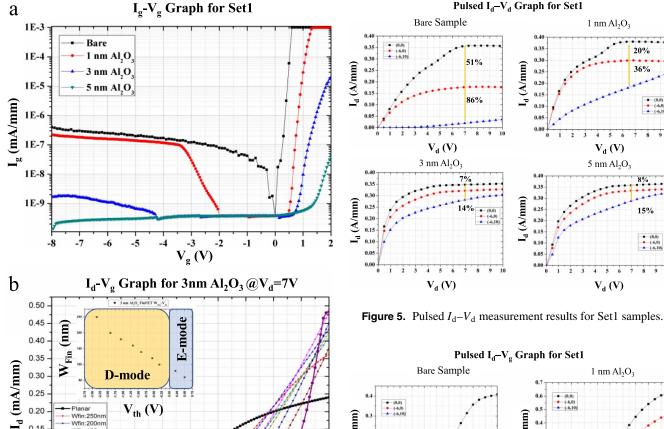

due to sidewall-gate depletion effect. Among all four cases, the first three samples (annotated as sample 1, sample 2 and sample 3) shows E-mode operation, while the last sample (i.e. sample 4) has D-mode functionality with a threshold voltage of -0.55 V. As expected, as the gate dielectric gets thicker, the fringing effects from the sidewalls lose their impact and full depletion cannot be acquired. In this sense, a thinner alumina layer is preferred. However, another factor that should be considered is the passivation property of such an ultrathin dielectric layer. To verify this,  $I_g-V_g$  characteristics of Fin-FET designs with and without gate dielectrics are studied, as depicted in figure 4(a). As it can be clearly seen from this panel, 1 nm thick layer has similar gate leakage response with the unpassivated design. According to the leakage and lag measurements, 1 nm thick layer cannot effectively passivate the dangling bonds, formed on the surface. However, 3 nm thick gate dielectric has unprecedentedly mitigated the gate leakage by above two orders of magnitude (at a gate bias of -5 V). Further increase in the dielectric thickness has not pronounced impact in the gate leakage suppression. Therefore, a fine trade-off between normally-off operation and gate passivation is achieved using 3 nm ultrathin Al<sub>2</sub>O<sub>3</sub> gate dielectric.

Further positive shift in  $V_{\rm th}$  can be accomplished by reducing the fin width. As the width shrinks, the sidewall depletion becomes more dominant and therefore more positive bias is required to build up the 2DEG density [48]. This can be seen in the normalized  $I_{\rm d}$ – $V_{\rm g}$  graph of FinFET designs with widths ranging from 250 nm to 60 nm, as shown in figure 4(b). It should be mentioned that all these results are obtained with 3 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric. As plotted in the inset, for fin widths below 100 nm the E-mode operation is realized. Although narrowing the fin structure can positively shift the  $V_{\rm th}$ , from the fabrication perspective, the dimension below 80 nm had repeatability and reliability issues. That is why, we chose 80 nm fin width as the optimal geometry.

As the drain current density, FinFET structures are 54% to 95% higher than planar structures at  $V_{\rm g}=+2$  V. Performance on some Fin widths differed from theoretical expectations due to deviation in fabrication such as drain-source distance, the position of gate and gate width variation or mismatch between the fin and footprint.

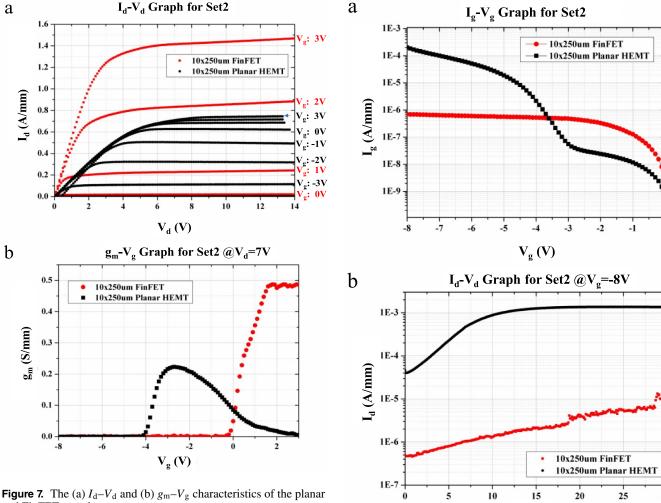

The double pulsed  $I_{\rm d}$ – $V_{\rm d}$  measurements are done to analyze drain and gate lag to see dynamic  $R_{\rm on}$  change, and the results are shown in figure 5. I–V measurements are performed by sweeping the pulsed drain voltage from 0 to 10 V under three quiescent points in order: Q(0 V, 0 V), Q(-6 V, 0 V), and Q(-6 V, 10 V). The gate and drain lag values are 51% and 86%, respectively, for the unpassivated sample. It is seen that dynamic Ron is increased dramatically in the stress condition of Q(-6 V, 10 V). The Lag performance of 1 nm  $Al_2O_3$  is between the unpassivated sample and 3 or 5 nm  $Al_2O_3$  samples which ensure that the GaN surface is not effectively passivated [26].

Moreover, the threshold voltage stability test is performed under the same quiescent voltage values sweeping the gate voltage from -8 V to +2 V while the drain voltage is +10 V. The results are shown in figure 6. While the reference sample

1 nm Al<sub>2</sub>O<sub>3</sub>

$V_d(V)$

5 nm Al<sub>2</sub>O<sub>3</sub>

**Table 1.**  $V_{\rm th}$  of the single gate device.

|                                               | Sample 1                  | Sample 2                                           | Sample 3                                           | Sample 4                                                  |

|-----------------------------------------------|---------------------------|----------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------|

| Type of device<br>Planar HEMT<br>80 nm FinFET | Bare<br>-3.48 V<br>0.56 V | 1 nm Al <sub>2</sub> O <sub>3</sub> -3.66 V 0.46 V | 3 nm Al <sub>2</sub> O <sub>3</sub> -3.82 V 0.20 V | 5 nm Al <sub>2</sub> O <sub>3</sub><br>-4.11 V<br>-0.55 V |

**Figure 4.** (a)  $I_g - V_g$  graph for Set1 samples, and (b)  $I_d - V_g$  graph for 3 nm Al<sub>2</sub>O<sub>3</sub> sample which is number 3.

$V_g(V)$

0.10 0.05

showed the biggest  $V_{th}$  shift (more than 0.6 V) performance, 3 and 5 nm Al<sub>2</sub>O<sub>3</sub> gate dielectric samples performed very stable  $V_{\rm th}$ . The 1 nm Al<sub>2</sub>O<sub>3</sub> sample's  $I_{\rm d}$ – $V_{\rm g}$  behavior looks like a bare sample.

# 3.2. DC and RF performance of ten-fingers devices

After optimization of device performance in a single-gate configuration, the next step, the design is scaled up to tenfingers multi-gate transistor, with a total gate periphery of 2.5 mm. In this set, again a reference planar HEMT is compared with the optimal FinFET structure with a fin width of

Pulsed I<sub>d</sub>-V<sub>d</sub> Graph for Set1

**Figure 6.** Pulsed  $I_d$ – $V_d$  measurement results for Set1 samples.

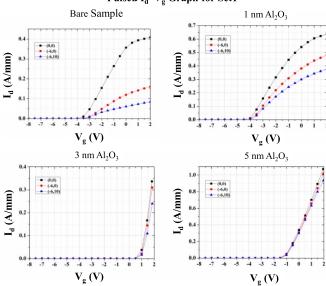

80 nm and alumina thickness of 3 nm. Figure 7(a) shows  $I_{\rm d}$ - $V_{\rm d}$  characteristics of these two under different gate bias voltages between -8 V to +3 V. The FinFET design demonstrates a maximum drain current of 1.43 A mm<sup>-1</sup> at 10 V drain and +3 V gate bias, while that for planar HEMT is found to be 0.74 A mm<sup>-1</sup>. This means FinFET current density 95%

and FinFET samples.

higher than planar device. It is worth noting that, to completely eliminate 2DEG in the multi mesa region, total gate width normalization is done for the FinFETs.

Additionally, the  $G_{\rm m}$ - $V_{\rm gs}$  characteristics of these samples at  $V_{\rm d} = 10$  V have been extracted, illustrated in figure 7(b). The FinFET sample gives a maximum  $g_m$  of  $\sim$ 490 mS mm<sup>-1</sup>, while this value for reference planar design is found to be 230 mS mm<sup>-1</sup>. Also, the linearity improvement has been achieved in the FinFET configuration. Compare to planar HEMT bell-shaped transconductance, FinFET's linearity refers to reducing the source resistance in the linear region and linear source and drain resistances. In the planar device, source resistance is increased with increasing the drain current [49–51]. As these graphs imply, the FinFET architecture has almost two-fold larger maximum drain current and conductance, in comparison with planar HEMT reference design. This remarkable improvement could be attributed to reduced thermal resistance in FinFETs stemming from additional lateral heat spreading of sidewall gates. The FinFET device also offers better electrostatic control of the gate. Moreover, the passivation property of the alumina layer reduces the density of trap states in vicinity of the 2DEG channel.

Another important factor, defining the overall performance of the transistor is its gate and drain leakages. As we can see

**Figure 8.** The (a)  $I_g$ – $V_g$  graph and (b) drain leakage current for gate bias of -8 V in both planar and FinFET configurations.

$V_{d}(V)$

from figure 8(a), the gate leakage in bias values below -4 Vare significantly lower than that of planar design. The higher leakage values in lower voltage values could be attributed to lower Schottky barrier formed between gate and GaN, compared to the one formed between gate and AlGaN. Moreover, the drain leakage has been also significantly suppressed in the FinFET configuration, owing to a better gate control in this configuration, see figure 8(b).

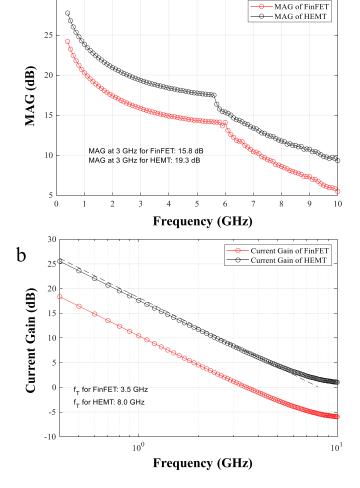

After completing the DC measurements, RF and largesignal measurements were done on the wafer to see and compare the performance of the devices. Small-signal measurements are performed for Set2 samples, with a drain voltage of 45 V and 40 mA drain current. Maximum available gain (MAG) is measured as 15.8 and 19.3 dB at 3 GHz for the FinFET and planar devices and, respectively, shown in figure 9(a). The cut-off frequency of the devices is also calculated from S-parameters. For the same bias conditions, the planar-gate (ft: 8 GHz) transistor over-performed FinFET devices ( $f_t$ : 3.5 GHz), as seen in figure 9(b). This performance can be explained by the higher parasitic capacitance of FinFET coming from the trench region and sidewall gates [52].

a

30

Figure 9. MAG and  $f_t$  characteristics of FinFET and planar HEMT.

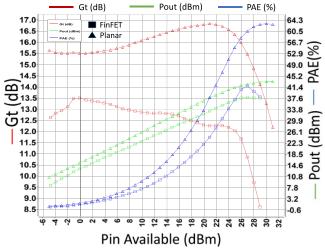

For the large-signal measurements, Class AB operation is selected for samples with a bias voltage of V<sub>ds</sub>: 45 V and quiescent  $I_{DO}$ : 16 mA mm<sup>-1</sup> with 15% duty cycle at 3.1 GHz at room temperatures. The gain,  $P_{\text{out}}$ , and power-added efficiency results are given in figure 10 which presents the results for FinFET (square) and planar (triangle). Planar HEMT shows a small-signal gain of 15.5 dB, while HEMT with Fin has a gain of 10.8 dB. On the other hand, HEMT with Fin gives a saturated  $P_{\text{out}}$  of 37.85 dBm (6.1 W), while the planar sample gives a saturated  $P_{\text{out}}$  of 43.05 dBm (20.2 W) at 3.0 dB gain compression. Considering the total effective gate width as a  $W_{\text{fin}} = 80 \text{ nm}$  and  $W_{\text{trench}} = 320 \text{ nm}$  for 400 nm period, accumulating a total effective gate width of  $W_{\rm eff} = 500~\mu{\rm m}$ , FinFET has a 12.2 W mm<sup>-1</sup> output power density, and planar is almost 8 W mm<sup>-1</sup>. FinFET results in 4.2 W mm<sup>-1</sup> of more output power density. These measurements yield an increase in  $P_{\text{out}}$  performance at FinFET at the same level of gain compression compared to the planar device.

The threshold voltage stability is important for devices when it comes to high power applications, as the performance of the transistor should be stable with high input power levels. To see this performance, three power sweep measurements are taken back-to-back for both devices. The forward gate currents

Figure 10. Power characteristics of FinFET and planar HEMT.

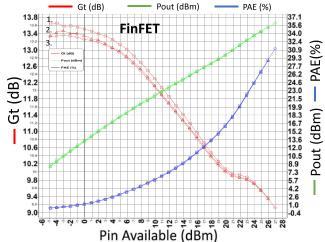

**Figure 11.** Three power sweep measurements for the sample with FinFET.

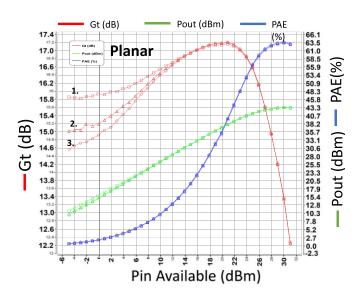

are observed during the measurements. For FinFET, the small-signal gain performance is stable after giving 27 dBm input power to the transistor, as no gain degradation is seen for the second and third measurements (figure 11). The gate current increases up to 70 mA (140 mA mm $^{-1}$ ) during this measurement, while the transistor is not saturated yet. For the planar device, after the first and second power sweep measurements up to 31 dBm, small-signal gain degraded by 0.8 dB and 0.5 dB. With 31 dBm input power, the forward gate current of planar HEMT increases to 17 mA (6.8 mA/mm). The degradation of the small-signal gain is due to the shift in  $V_{\rm th}$  with high power levels, which is not desired in high power applications, as transistors need to endure very high input power levels. (figure 12).

Many papers have been reported on the GaN FinFET technology since 2009. A general review and perspective of Gan FinFETs were reported bu Zhang *et al* [18]. Lateral AlGaN/GaN power FinFET transistors are focused on the benchmark.

**Figure 12.** Three power sweep measurements for the sample with Planar HEMT.

Table 2. Comparison of Laterally AlGaN/GaN FinFETs.

| Reference | Year | Mode | Device size (um) | DC performance                                                                                                                                                                     | RF performance                                   |

|-----------|------|------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| [45]      | 2015 | D    | 2 × 50           | I <sub>ds</sub> : 2200 mA mm <sup>-1</sup><br>(+%69)<br>G <sub>m</sub> : 750 mS mm <sup>-1</sup><br>(+%66)                                                                         | Pout: NR                                         |

| [17]      | 2017 | D    | 2 × 125          | $I_{\rm g}$ : <10 <sup>-6</sup> A mm <sup>-1</sup><br>$I_{\rm ds}$ : 1640 mA mm <sup>-1</sup><br>(+%145)<br>$G_{\rm m}$ : NR<br>$I_{\rm g}$ : <10 <sup>-4</sup> A mm <sup>-1</sup> | Pout: 11.3 W mm <sup>-1</sup> (+%66) @8 GHz      |

| [53]      | 2019 | Е    | 25               | $I_{\rm g}$ : <10 A mm $I_{\rm ds}$ : 896 mA mm <sup>-1</sup> (-%48) $G_{\rm m}$ <200 mS mm <sup>-1</sup> (-%10) $I_{\rm g}$ : <10 <sup>-6</sup> A mm <sup>-1</sup>                | Pout: NR                                         |

| [54]      | 2022 | Е    | 50               | $I_{ds}$ : 1121 mA mm <sup>-1</sup><br>(+%109)<br>$G_{m}$ : 185 mS mm <sup>-1</sup><br>(+%125)<br>$I_{g}$ : <10 <sup>-6</sup> A mm <sup>-1</sup>                                   | Pout: NR                                         |

| This Work | 2022 | Е    | 10 × 250         | $I_{\text{ds}}$ : 1430 mA mm <sup>-1</sup><br>(+%93)<br>$G_{\text{m}}$ : 490 mS mm <sup>-1</sup><br>(+%115)<br>$I_{\text{g}}$ : <10 <sup>-6</sup> A mm <sup>-1</sup>               | Pout: 12.2 W mm <sup>-1</sup> (+%52)<br>@3.1 GHz |

NR, not reported.

Table 2 summarizes the E/D mode, size and electrical characterization of AlGaN/GaN FinFETs. The DC and RF performance of the device is affected by the Fin structure and fabrication, as well as the %Al and thickness of AlGaN, drainsource length, gate type and footprint. Therefore, the comparison with the planar device and FinFET is more important for the same process. The difference with the planar device is also shown.

From the comparison, the largest E mode transistor was fabricated in the literature. As a result of the power performance and three-point reliability measurements of the

device operating at the AB class S-band, promising results were obtained for power applications. By further reducing trench size, more power can be obtained in the same size device.

#### 4. Conclusion

In this paper, the influences of the fin width and ultrathin  $Al_2O_3$  gate dielectric on the DC and RF characteristics of FinFET and planar AlGaN/GaN HEMTs have been

investigated. Considerable threshold voltage shift was achieved with decreasing the channel width, moving the threshold voltage from -3.7 V (for planar design) to 0.2 V(for FinFET design). It was found that in a 2.5 mm device periphery, 80 nm Fin width, and 3 nm gate dielectric thickness, a reliable E-mode operation can be achieved in FinFET design. The optimized has superior DC performance with near two times larger drain current and conductance values. The obtained value of leakage current density is two orders lower than the conventional HEMTs for the gate voltage of -8 Vand the drain voltage of 30 V. FinFET with these optimized geometries reveals 4.2 W mm $^{-1}$  more  $P_{\text{out}}$  performance at the same level of gain compression compare to a planar device. The large signal measurements of the devices confirm that FinFET has an increase of Pout density by over 50% compared to planar device. As a gain degradation, FinFET shows perfect stable performance, compared to that of planar HEMT. With this advantage, FinFET could be seen at commercial device levels in high power applications in the coming years.

# Data availability statement

All data that support the findings of this study are included within the article (and any supplementary files).

# **Acknowledgments**

The authors would like to express gratitude to the fabrication team and RF group at NANOTAM. Special thanks to Dr Amir Ghobadi for his valuable technical support.

# **ORCID iDs**

Ekmel Özbay https://orcid.org/0000-0003-2953-1828 Semsettin Altındal https://orcid.org/0000-0001-7880-2618

#### References

- [1] Mishra U K, Parikh P and Yi-Feng W 2002 AlGaN/GaN HEMTs-an overview of device operation and applications Proc. IEEE 90 1022–31

- [2] Nahhas A M 2019 Review of AlGaN/GaN HEMTs based devices Am. J. Nanomater. 7 10–21

- [3] Palacios T, Chakraborty A, Rajan S, Poblenz C, Keller S, DenBaars S P, Speck J S and Mishra U K 2005 High-power AlGaN/GaN HEMTs for Ka-band applications *IEEE* Electron Device Lett. 26 781–3

- [4] Ambacher O, Foutz B, Smart J, Shealy J R, Weimann N G, Chu K, Murphy M, Sierakowski A J, Schaff W J and Eastman L F 2000 Two-dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped

- and doped AlGaN/GaN heterostructures *J. Appl. Phys.* **87** 334–44

- [5] Roccaforte F, Greco G, Fiorenza P and Iucolano F 2019 An overview of normally-Off GaN-based high electron mobility transistors *Materials* 12 1599

- [6] Liu S et al 2012 Enhancement-mode operation of nanochannel array (NCA) AlGaN/GaN HEMTs IEEE Electron Device Lett. 33 354–6

- [7] Chen K J and Zhou C 2011 Enhancement-mode AlGaN/GaN HEMT and MIS-HEMT technology *Phys. Status Solidi* a 208 434–8

- [8] Kurt G, Gulseren M, Salkim G, Ural S, Kayal O, Ozturk M, Butun B, Kabak M and Ozbay E 2019 Investigation of a hybrid approach for normally-off GaN HEMTs using fluorine treatment and recess etch techniques *IEEE J. Electron Devices Soc.* 7 351–7

- [9] Si Q, Yue H, Xiaohua M, Yuanbin X and Jigang M 2009 Enhancement-mode AlGaN/GaN HEMTs fabricated by fluorine plasma treatment J. Semiconduct. 30 124002–4

- [10] Gao Z, Hou B, Liu Y and Ma X 2016 Impact of fluorine plasma treatment on AlGaN/GaN high electronic mobility transistors by simulated and experimental results *Microelectron. Eng.* 154 22–25

- [11] Giuseppe G, Giannazzo F, Frazzetto A, Raineri V and Roccaforte F 2011 Near-surface processing on AlGaN/GaN heterostructures: a nanoscale electrical and structural characterization Nanoscale Res. Lett. 6 132

- [12] Strang B S 2012 Fabrication and characterization of gallium nitride based high electron mobility transistors for mm-wave applications *PhD dissertation of Physik* Fachgruppe Physik, RWTH Aachen University, Aachen, Germany

- [13] Meneghini M, Hilt O, Wuerfl J and Meneghesso G 2017 Technology and reliability of normally-Off GaN HEMTs with p-type gate *Energies* 10 153

- [14] Wu T-L, Marcon D, You S, Posthuma N, Bakeroot B, Stoffels S, van Hove M, Groeseneken G and Decoutere S 2015 Forward bias gate breakdown mechanism in enhancement-mode p-GaN Gate AlGaN/GaN high-electron mobility transistors *IEEE Electron Device Lett.* 36 1001–3

- [15] Wang W, Li Y, Lin C, Chan Y, Chen G and Chyi J 2004 Low damage, Cl2-based gate recess etching for 0.3-μm gate-length AlGaN/GaN HEMT fabrication *IEEE Electron* Device Lett. 25 52–54

- [16] Ohi K and Hashizume T 2009 Drain current stability and controllability of threshold voltage and subthreshold current in a multi-mesa-channel AlGaN/GaN high electron mobility transistor *Jpn. J. Appl. Phys.* 48 08JA03

- [17] Zhang K, Kong Y, Zhu G, Zhou J, Yu X, Kong C, Li Z and Chen T 2017 High-linearity AlGaN/GaN FinFETs for microwave power applications *IEEE Electron Device Lett.* 38 615–8

- [18] Zhang Y, Zubair A, Liu Z, Xiao M, Perozek J, Ma Y and Palacios T 2021 GaN FinFETs and trigate devices for power and RF applications: review and perspective Semicond. Sci. Technol. 36 054001

- [19] Ture E, Brückner P, Quay R, Ambacher O, Alsharef M, Granzner R and Schwierz F 2016 Enhancement-mode AlGaN/GaN FinFETs with high on/off performance in 100 nm gate length 2016 11th European Microwave Integrated Circuits Conf. (Eumic) pp 61–64

- [20] Chang L, Lin J, Dai C, Yang M, Jiang Y, Wu Y and Wu C 2019 Systematic investigation of the threshold voltage modulation of AlGaN/GaN Schottky-gate Fin-HEMTs J. Appl. Phys. 125 094502

- [21] Lu B, Matioli E and Palacios T 2012 Tri-gate normally-Off GaN power MISFET IEEE Electron Device Lett. 33 360–2

- [22] Ture E, Brückner P, Raay F V, Quay R, Ambacher O, Alsharef M, Granzner R and Schwierz F 2015 Performance

- and parasitic analysis of sub-micron scaled tri-gate Al%GaN/GaN HEMT design 2015 10th European Microwave Integrated Circuits Conf. (Eumic) pp 97–100

- [23] Yadav C, Kushwaha P, Khandelwal S, Duarte J P, Chauhan Y S and Hu C 2014 Modeling of GaN-based normally-Off FinFET IEEE Electron Device Lett. 35 612–4

- [24] Odabaşı O, Yılmaz D, Aras E, Asan K E, Zafar S, Akoğlu B C, Bütün B and Özbay E 2021 AlGaN/GaN-based laterally gated high-electron-mobility transistors with optimized linearity *IEEE Trans. Electron Devices* 68 1016–23

- [25] Soman R, Raghavan S and Bhat N 2018 Normally off AlGaN/GaN FinFET devices on Si substrate 2018 4th IEEE Int. Conf. on Emerging Electronics (ICEE) pp 1–4

- [26] Jo Y, Son D, Won C, Im K-S, Seo J, Kang I and Lee J-H 2015 AlGaN/GaN FinFET with extremely broad transconductance by side-wall wet etch *IEEE Electron* Device Lett. 36 1008–10

- [27] Zhou X et al 2017 Dynamic characteristics and related trapping effects of GaN-based Fin-MISHEMTs 2017 IEEE 12th Int. Conf. on ASIC (ASICON) pp 584–7

- [28] Zhang M, Ma X, Mi M, He Y, Hou B, Zheng J, Zhu Q, Chen L, Zhang P and Yang L 2017 Improved on-state performance of AlGaN/GaN Fin-HEMTs by reducing the length of the nanochannel Appl. Phys. Lett. 110 193502

- [29] Im K, Won C, Jo Y, Lee J, Bawedin M, Cristoloveanu S and Lee J 2013 High-performance GaN-based nanochannel FinFETs with/without AlGaN/GaN heterostructure *IEEE Trans. Electron Devices* 60 3012–8

- [30] Ma J and Matioli E 2017 High performance tri-gate GaN power MOSHEMTs on silicon substrate *IEEE Electron Device Lett.* **38** 367–70

- [31] Tang C, Teo K H and Shi J 2017 Simulation of GaN HEMT with wide-linear-range transconductance 2017 Int. Conf. on Electron Devices and Solid-State Circuits (EDSSC) pp 1–2

- [32] Nguyen P D, Clavel M B, Liu J and Hudait M K 2017 Investigating FinFET sidewall passivation using epitaxial (100)Ge and (110)Ge metal–oxide–semiconductor devices on AlAs/GaAs IEEE Trans. Electron Devices 64 4457–65

- [33] Ma Y *et al* 2021 Kilovolt tri-gate GaN junction HEMTs with high thermal stability 2021 33rd Int. Symp. on Power Semiconductor Devices and ICs (ISPSD) pp 139–42

- [34] Jang Y, Shin S, Yi S and Hong M 2019 A single gas barrier layer of high-density Al<sub>2</sub>O<sub>3</sub> formed by neutral beam-assisted sputtering at room temperature *Thin Solid* Films 674 52

- [35] Groner M D, Elam J W, Fabreguette F H and George S M 2002 Electrical characterization of thin Al<sub>2</sub>O<sub>3</sub> films grown by atomic layer deposition on silicon and various metal substrates *Thin Solid Films* 413 186

- [36] Hong M et al 2000 Properties of Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/GaNGa<sub>2</sub>O<sub>3</sub> (Gd<sub>2</sub>O<sub>3</sub>)/GaN metal-insulator-semiconductor diodes J. Vac. Sci. Technol. B 18 1453

- [37] Chang Y, Chiu H, Lee Y, Huang M, Lee K, Chiu Y, Wang Y, Kwo J and Hong M 2007 Structural and electrical characteristics of atomic layer deposited high k HfO<sub>2</sub> on GaN Appl. Phys. Lett. 90 232904

- [38] Ye G, Wang H, Arulkmaran S, Ng G, Li Y, Liu Z and Ang K 2014 Surface band bending and band alignment of plasma enhanced atomic layer deposited dielectrics on Ga- and N-face gallium nitride Appl. Phys. Lett. 105 022106

- [39] Ye D, Yang B, Ng K, Bude J, Wilk G, Halder S and Hwang J 2005 GaN metal-oxide-semiconductor high-electron-mobility-transistor with atomic layer deposited Al2O3Al2O3 as gate dielectric Appl. Phys. Lett. 86 063501

- [40] Wilk G, Wallace R and Anthony J 2001 High-κ gate dielectrics: current status and materials properties considerations J. Appl. Phys. 89 5243

- [41] Zhang M et al 2018 Threshold voltage control for AlGaN/GaN Fin-HEMTs with combined technologies 2018 1st Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia) pp 110–3

- [42] Boukortt N E I, Lenka T R, Patanè S and Crupi G 2022 Effects of varying the fin width, fin height, gate dielectric material, and gate length on the DC and RF performance of a 14-nm SOI FinFET structure *Electronics* 11 91

- [43] Ma J, Santoruvo G, Nela L, Wang T and Matioli E 2019 Impact of Fin width on tri-gate GaN MOSHEMTs *IEEE Trans. Electron Devices* **66** 4068–74

- [44] Ma Y, Xiao M, Du Z, Wang H and Zhang Y 2021 Tri-gate GaN junction HEMTs: physics and performance space *IEEE Trans. Electron Devices* **68** 4854–61

- [45] Ture E et al 2016 High-current submicrometer tri-gate GaN high-electron mobility transistors with binary and quaternary barriers IEEE J. Electron Devices Soc. 4 1–6

- [46] Azize M and Palacios T 2011 Top-down fabrication of AlGaN/GaN nanoribbons Appl. Phys. Lett. 98 042103

- [47] Zhou X et al 2018 Dynamic characteristics of AlGaN/GaN Fin-MISHEMTs with Al2O3 dielectric IEEE Trans. Electron Devices 65 928–35

- [48] Ohi K, Asubar J T, Nishiguchi K and Hashizume T 2013 Current stability in multi-mesa-channel AlGaN/GaN HEMTs IEEE Trans. Electron Devices 60 2997–3004

- [49] Chen C-H 2016 The causes of GaN HEMT bell-shaped transconductance degradation *Solid State Electron*. 126 115–24

- [50] Lee D S et al 2013 Nanowire channel InAlN/GaN HEMTs with high linearity of gm and ft IEEE Electron Device Lett. 34 969–71

- [51] Trew R J, Liu Y, Bilbro L, Kuang W, Vetury R and Shealy J B 2006 Nonlinear source resistance in high-voltage microwave AlGaN/GaN HFETs IEEE Trans. Microw. Theory Tech. 54 2061–7

- [52] Alsharef M et al 2016 RF performance of Trigate GaN HEMTs IEEE Trans. Electron Devices 63 4255–61

- [53] Wu C-H *et al* 2019 Normally-off tri-gate GaN MIS-HEMTs with 0.76 mΩ·cm2 specific on-resistance for power device applications *IEEE Trans. Electron Devices* **66** 3441–6

- [54] Tsai C-J et al 2021 High-performance normally-off recessed tri-gate GaN MIS-FETs in micrometer scale Semicond. Sci. Technol. 37 015002