## Enhanced memory effect with embedded graphene nanoplatelets in ZnO charge trapping layer

Nazek El-Atab, Furkan Cimen, Sabri Alkis, Ali K. Okyay, and Ammar Nayfeh

Citation: Applied Physics Letters **105**, 033102 (2014); doi: 10.1063/1.4891050

View online: http://dx.doi.org/10.1063/1.4891050

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/105/3?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Enhanced memory effect via quantum confinement in 16 nm InN nanoparticles embedded in ZnO charge trapping layer

Appl. Phys. Lett. 104, 253106 (2014); 10.1063/1.4885397

Tuning of undoped ZnO thin film via plasma enhanced atomic layer deposition and its application for an inverted polymer solar cell

AIP Advances 3, 102114 (2013); 10.1063/1.4825230

Electrical transport and Al doping efficiency in nanoscale ZnO films prepared by atomic layer deposition J. Appl. Phys. **114**, 024308 (2013); 10.1063/1.4813136

Vertically aligned ZnO nanostructures grown on graphene layers

Appl. Phys. Lett. 95, 213101 (2009); 10.1063/1.3266836

Low-temperature growth of ZnO nanorods in anodic aluminum oxide on Si substrate by atomic layer deposition Appl. Phys. Lett. **90**, 033104 (2007); 10.1063/1.2431786

## Enhanced memory effect with embedded graphene nanoplatelets in ZnO charge trapping layer

Nazek El-Atab, <sup>1</sup> Furkan Cimen, <sup>2</sup> Sabri Alkis, <sup>3,4</sup> Ali K. Okyay, <sup>2,3,4</sup> and Ammar Nayfeh <sup>1</sup> Department of Electrical Engineering and Computer Science (EECS), Institute Center for Microsystems–iMicro, Masdar Institute of Science and Technology, Abu Dhabi, United Arab Emirates <sup>2</sup> Department of Electrical and Electronics Engineering, Bilkent University, Ankara 06800, Turkey <sup>3</sup> UNAM-National Nanotechnology Research Center, Bilkent University, Ankara 06800, Turkey <sup>4</sup> Institute of Materials Science and Nanotechnology, Bilkent University, Ankara 06800, Turkey

(Received 28 April 2014; accepted 13 July 2014; published online 21 July 2014)

A charge trapping memory with graphene nanoplatelets embedded in atomic layer deposited ZnO (GNIZ) is demonstrated. The memory shows a large threshold voltage  $V_t$  shift (4 V) at low operating voltage (6/-6 V), good retention (>10 yr), and good endurance characteristic (>10<sup>4</sup> cycles). This memory performance is compared to control devices with graphene nanoplatelets (or ZnO) and a thicker tunnel oxide. These structures showed a reduced  $V_t$  shift and retention characteristic. The GNIZ structure allows for scaling down the tunnel oxide thickness along with improving the memory window and retention of data. The larger  $V_t$  shift indicates that the ZnO adds available trap states and enhances the emission and retention of charges. The charge emission mechanism in the memory structures with graphene nanoplatelets at an electric field  $E \ge 5.57$  MV/cm is found to be based on Fowler-Nordheim tunneling. The fabrication of this memory device is compatible with current semiconductor processing, therefore, has great potential in low-cost nano-memory applications. © 2014 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4891050]

In the past decade, memory chips with low-cost, low-power consumption, and high density have gained tremendous attention due to the growing market of consumer electronic equipment such as smartphone, tablet, mobile internet devices, and digital cameras. However, current nonvolatile flash memory devices are facing major challenges to maintain their good reliability and retention with the continuous increase in density and scaling of the gate length. Therefore, it is imperative to find novel structures and materials to be incorporated in the memory cells which would allow tunnel oxide and voltage scaling.

Recently, two-dimensional graphene and its derived nanomaterials have attracted great efforts and research due to their exceptional characteristics such as high carrier mobility, large work-function, thermal conductivity, structural robustness, and optical transparency.<sup>3,4</sup> Based on these unique electronic properties, graphene appears to be a promising material in nonvolatile memory devices. Graphene flash memory with large memory window and low voltage has been demonstrated, where graphene sheets were used as the floating gate of the memory.<sup>5</sup> However, this type of memory is less efficient and has a single point of failure because if a defect exists in the tunnel oxide, then all the stored charge in the floating gate would leak out. In this paper, we demonstrate the use of graphene nanoplatelets embedded in a ZnO layer (GNIZ) as the charge storage media in charge trapping memory devices. The performance of this device is compared to the control devices with only ZnO or graphene nanoplatelets (GN) charge storage layer with a thicker tunnel oxide in order to show the effect of GNIZ on the retention and endurance characteristics of the memory.

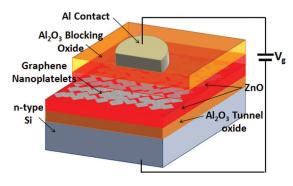

The MOS memory cells are fabricated on an  $n^+$ -type (111) (Antimony doped, 15–20 m $\Omega$ -cm) Si wafer. First, 3.6-nm-thick tunnel oxide Al<sub>2</sub>O<sub>3</sub> followed by 2-nm-thick

ZnO are deposited at 250 °C using Cambridge Nanotech Savannah-100 atomic layer deposition (ALD) system. Pristine graphene nanoplatelets (NanoIntegris PureSheets Quattro grade) are deposited by drop-casting technique. Samples are placed on hot-plate at 110 °C and 2-2.5 ml of 0.05 mg/ml graphene solution is drop-casted slowly by using plastic pipette and samples are left to dry for 5 min on hotplate. Then a 2-nm-thick ZnO followed by a 15-nm-thick Al<sub>2</sub>O<sub>3</sub> blocking oxide are ALD deposited at 250 °C. Finally, a 400-nm-thick Al layer with a diameter of 1 mm is sputtered using a shadow mask for the gate contact. A cross-sectional illustration of the fabricated memory device structure is depicted in Figure 1(a). The control structure with only GN (or only 4-nm ZnO) is fabricated the same way but with a 5-nm-thick tunnel oxide. Moreover, it should be noted that although the fabricated memory devices have 1-mm diameter, according to the ITRS roadmap the structure of such MOS memory device is expected to be scalable without degradation of performance.

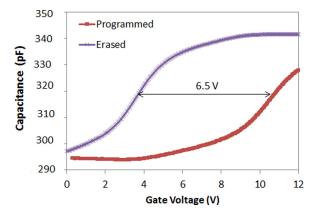

The charging effect in the fabricated memory cells is analyzed by studying the high frequency (1 MHz) C-V<sub>gate</sub> curves of the programmed and erased states. Using the Agilent-Signatone B1505A device analyzer, the gate voltage of the memory cells is swept at  $-12/12\,\mathrm{V}$  backward and forward. The obtained memory hysteresis shows a 6.5 V, 5.5 V, and 0.9 V for the memories with GNIZ, GN, and ZnO charge trapping layer, respectively. The high frequency C-V measurement at  $12/-12\,\mathrm{V}$  for the memory structure depicted in Figure 1 is shown in Figure 2. The significant positive shift of the V<sub>FB</sub> of the erased state indicates that there is a significant amount of electrons trapped at the interfacial or in the oxide layer. In fact, the positive shift confirms the n-type nature of the ZnO layer which is due to crystallographic defects such as interstitial zinc and oxygen vacancies.  $^{6-12}$  In

FIG. 1. Cross sectional illustration of the fabricated MOS memory with GNIZ.

addition, by sweeping the gate voltage from 12 to -12 V, the C-V curve is observed to shift positively, which indicates that the memory is being programmed by trapping electrons in the charge storage layer.

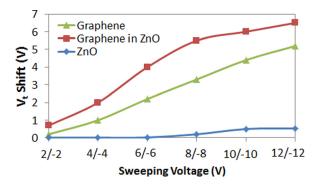

Moreover, the C-V hysteresis measurement is repeated on the three fabricated devices at different sweeping voltages. The obtained  $V_t$  shifts plotted in Figure 3 show that GNIZ memory provides the largest memory window. This is due to the thinner tunnel oxide, which exponentially increases the charge emission and tunneling probability, in addition to the additional trap states provided by the ZnO. Moreover, the figure shows that the memory with only ZnO layer does not provide a remarkable  $V_t$  shift even at high sweeping voltages  $(12/-12\,V)$ . This indicates that the ZnO in the GNIZ structure provides few additional trap states; however, it mainly enhances the electron retention in the graphene nanoplatelets by reducing the charge back-tunneling probability.

Since the ZnO is shown to provide only few trap states, the charge trap states density of the graphene nanoplatelets can be calculated by adopting the following equation: 11,13

$$N_t = \frac{C_t \times \Delta V_t}{q} \tag{1}$$

where  $C_t$  is the capacitance of the memory per unit area,  $\Delta V_t$  is the  $V_t$  shift, and q is the elementary charge. At  $6/-6\,V_t$  sweeping voltage, with a 4 V  $V_t$  shift, and  $C_t$  is 43.31 nF/cm<sup>2</sup>, the charge trap states density is roughly  $1.08\times10^{12}\,\mathrm{cm}^{-2}$ .

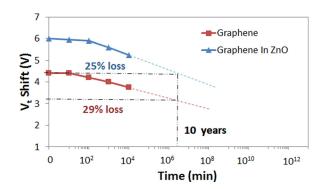

The virgin memory cell  $V_t$  shift is measured at room temperature and plotted vs. time as shown in Figure 4.

FIG. 2. C-V measurement at  $12/-12\,\mathrm{V}$  (forward and backward) of the memory with GNIZ. The measurement is done at room temperature.

FIG. 3. Measured  $V_{\rm t}$  shifts at different gate sweeping voltages for the three memory structures.

Usually, thinner tunnel oxides are associated with a degraded retention characteristic. However, the memory with GNIZ which has a 1.4 nm thinner tunnel oxide (35% thinner) showed an improved retention characteristic, where the extrapolation to 10 yr indicates a loss of 25% of the stored charge in the GNIZ memory while 29% in the GN memory. The retention measurements show that the use of ZnO in the charge storage media allows for further scaling of the tunnel oxide thickness without degrading the reliability or the retention properties of the memory.

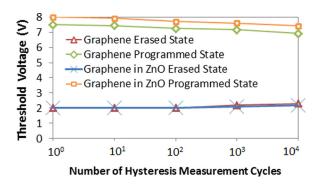

Furthermore, the endurance characteristic of the memories with GNIZ and GN are studied. A fresh memory cell hysteresis is measured at room temperature at  $10/-10\,\mathrm{V}$  forward and backward up to  $10^4$  cycles as shown in Figure 5. The  $V_t$  shift slightly reduced after  $10^4$  which proves the good endurance of such memory structure. In addition, the memory with GNIZ showed an improved endurance where its  $V_t$  shift reduced by 13.3%, while the memory with only GN showed a reduction of 17% after  $10^4$  memory hysteresis cycles.

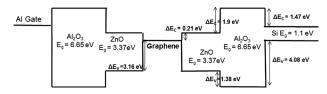

The energy band diagram of the structure with GNIZ is depicted in Figure 6 using the reported work-function, electron affinities, and bandgap of the different materials.  $^{7,14,15}$  The conduction band offset between the Si substrate and tunnel oxide is smaller than the valence band offset, which makes the electrons emission probability much higher  $(1.47 \, \text{eV} < 4.08 \, \text{eV})$ . This was proven in Figure 2, where the positive shift of the programmed state indicated electrons storage in the charge trapping layer.

Since the ZnO is observed to provide few trap states, then the majority of the electrons are expected to tunnel

FIG. 4.  $V_t$  shift vs. time extrapolated to 10 yr with GNIZ and GN charge trapping layer.

FIG. 5. Endurance measurement showing threshold voltage shift vs. number of hysteresis measurement cycles.

through the tunneling oxide to the ZnO layer and then be swept by the electric field and get trapped within the graphene nanoplatelets. Also, the additional thickness of the ZnO and the large conduction band offset between graphene and the tunnel oxide reduces the probability of backtunneling, which improves the retention characteristic of the memory as proven in Figure 4.

The electric field across the tunnel oxide of the memory with GN is calculated using the following Gauss's law: 16

$$\in_1 E_1 = \in_2 E_2 + Q,\tag{2}$$

$$V_g = V_1 + V_2 = d_1 E_1 + d_2 E_2, (3)$$

where  $\in$  is the dielectric permittivity, E is the electric field in the oxide, Q is the stored charge in the graphene nanoplatelets, V is the voltage across the oxide, d is the oxide thickness, and the subscripts 1 and 2 correspond to the tunnel and blocking oxides, respectively. The resulting electric field through the tunnel oxide is the following:

$$E_{1} = \frac{V_{g}}{d_{1} + d_{2} \left(\frac{\epsilon_{1}}{\epsilon_{2}}\right)} + \frac{Q}{\epsilon_{1} + \epsilon_{2} \left(\frac{d_{1}}{d_{2}}\right)}.$$

(4)

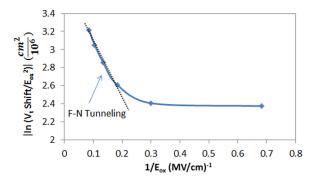

The natural logarithm of the  $V_t$  shift divided by the square of the electric field is plotted vs. the reciprocal of the electric field as shown in Figure 7. The linear trend indicates that the dominant electron emission mechanism at an electric field in the tunnel oxide  $E \geq 5.57\,$  MV/cm (corresponding to a 6 V gate voltage) is Fowler-Nordheim tunneling (F-N). In F-N tunneling, the charges are injected by tunneling into the conduction band of the oxide through a triangular energy barrier and then are swept by the electric field into the charge trapping layer. The emission rate of charges in F-N tunneling follows the equation:  $^{16}$

FIG. 6. Energy band diagram of the memory with GNIZ charge trapping layer. The large conduction band offset between graphene and tunnel oxide exponentially reduces the charge leakage.

FIG. 7. Plot showing the natural logarithm of the  $V_t$  shift divided by the square of the electric field is plotted vs. the reciprocal of the electric field. The linear trend indicates that Fowler-Nordheim is the dominant emission mechanism at an oxide electric field of 5.57 MV/cm.

$$J = C_1 E_{ox}^2 e^{-\frac{C2}{E_{ox}}},\tag{5}$$

where J is the F-N tunneling current,  $E_{ox}$  is the electric field across the tunnel oxide, and  $C_1$  and  $C_2$  are constants in terms of the effective mass and barrier height.

However, the addition of ZnO to the charge storage media will affect the electric field. Since the ALD ZnO is n-type, the electric field across the tunnel oxide is expected to be smaller than in the case of the GN structure. However, in the case of the GNIZ memory, the tunnel oxide thickness is 1.4 nm thinner, which would increase the electric field linearly and electron tunneling probability exponentially. Based on the larger V<sub>t</sub> shifts obtained with GNIZ, as shown in Figure 3, the electric field and tunneling probability through the tunnel oxide are expected to be higher than that in the GN case. However, in CMOS technology, <sup>17,18</sup> F-N is considered as the tunneling mechanism which requires the highest electric field, therefore, F-N tunneling is expected to be the dominant electron emission mechanism in the memory with GNIZ as well. As a result, the retention of the MOS memory structure with graphene-nanoplatelets embedded in ZnO is expected to be independent of temperature since F-N tunneling is independent of temperature. 19 This have been demonstrated in Ref. 19, where the retention of fabricated Metal-Al<sub>2</sub>O<sub>3</sub>-Nitride-Al<sub>2</sub>O<sub>3</sub>-Semiconductor (MANAS) memory devices is insensitive to temperature and the main mechanism is F-N tunneling.

In conclusion, the use of graphene nanoplatelets in the charge storage media in charge trapping memory is demonstrated. With GN, the memory device showed a large  $V_t$  shift at  $10/-10\,V$ , good retention, and endurance characteristics. The use of a thinner tunnel oxide and the addition of ZnO to the charge storage media showed an improved performance of the memory, where  $4\,V\,V_t$  shift is achieved at  $6/-6\,V$ , with an expected loss of 25% of stored charges after 10 yr, and an endurance greater than  $10^4$  memory hysteresis cycle. The emission mechanism in such memory devices at electric fields higher than  $5.57\,MV/cm$  is found to be dominated by Fowler-Nordheim tunneling. Finally, this work shows that graphene nanoplatelets are a good candidate for charge trapping layers in future low-power and low-cost nonvolatile memory devices.

We gratefully acknowledge financial support for this work provided by the Masdar Institute of Science and

Technology and the Advanced Technology Investment Company (ATIC). This work was supported in part by TUBITAK Grant Nos. 109E044, 112M004, 112E052, and 113M815.

- <sup>1</sup>International Technology Roadmap for Semiconductor Industry (ITRS), San Jose, California, 2009.

- <sup>2</sup>C. Y. Lu, K. Y. Hsieh, and R. Liu, Microelectron. Eng. **86**, 283–286 (2009).

- <sup>3</sup>K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science **306**, 666–669 (2004).

- <sup>4</sup>F. Schwierz, Nat. Nanotechnol. 5, 487–496 (2010).

- <sup>5</sup>S. Wang, J. Pu, D. S. H. Chan, B. J. Cho, and K. P. Loh, Appl. Phys. Lett. **96**, 143109 (2010).

- <sup>6</sup>N. El-Atab, S. Alqatari, F. B. Oruc, T. Souier, M. Chiesa, A. K. Okyay, and A. Nayfeh, AIP Adv. 3, 102119–102126 (2013).

- <sup>7</sup>N. El-Atab, A. Rizk, A. Okyay, and A. Nayfeh, AIP Adv. 3, 112116 (2013).

- <sup>8</sup>N. El-Atab, A. Ozcan, S. Alkis, A. K. Okyay, and A. Nayfeh, Appl. Phys. Lett. **104**, 013112 (2014).

- <sup>9</sup>F. B. Oruc, F. Cimen, A. Rizk, M. Ghaffari, A. Nayfeh, and A. K. Okyay, IEEE Electron Device Lett. **33**, 1714–1716 (2012).

- <sup>10</sup>N. El-Atab, A. Ozcan, S. Alkis, A. K. Okyay, and A. Nayfeh, Phys. Status Solidi RRL 8, 629–633 (2014).

- <sup>11</sup>N. El-Atab, F. Cimen, S. Alkis, B. Ortaç, M. Alevli, N. Dietz, A. K. Okyay, and A. Nayfeh, Appl. Phys. Lett. **104**, 253106 (2014).

- <sup>12</sup>S. Alkis, B. Tekcan, A. Nayfeh, and A. K. Okyay, J. Opt. **15**, 105002 (2013).

- <sup>13</sup>W. Liu, C. L. Cheng, S. W. Huang, J. T. Jeng, S. H. Shiau, and B. T. Dai, Appl. Phys. Lett. **91**, 042107–042110 (2007).

- <sup>14</sup>Y. J. Yu, Y. Zhao, S. Ryu, L. E. Brus, K. S. Kim, and P. Kim, Nano Lett. 9, 3430–3434 (2009).

- <sup>15</sup>S. S. Datta, D. R. Strachan, E. J. Mele, and A. T. C. Johnson, Nano Lett. 9, 7–11 (2009).

- <sup>16</sup>S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3rd ed., (John Wiley & Sons, JNC, 2007).

- <sup>17</sup>E. Miranda, J. Molina, Y. Kim, and H. Iwai, J. Non-Cryst. Solids 352, 92 (2006).

- <sup>18</sup>W. C. Lee and C. Hu, IEEE Trans. Electron Devices **48**, 1366 (2001).

- <sup>19</sup>D. S. Eun, Ph.D. dissertation, EE, Yale University, New Haven, Connecticut 06520, USA, 2011.